# 저전력지능형 반도체 소자를 위한 물질 및 기술

https://www.unr.edu/engineering/about/news/magazine/2020/wpeb

# Semiconductor Materials and Devices for Low-power Artificial Intelligent Semiconductor Chips

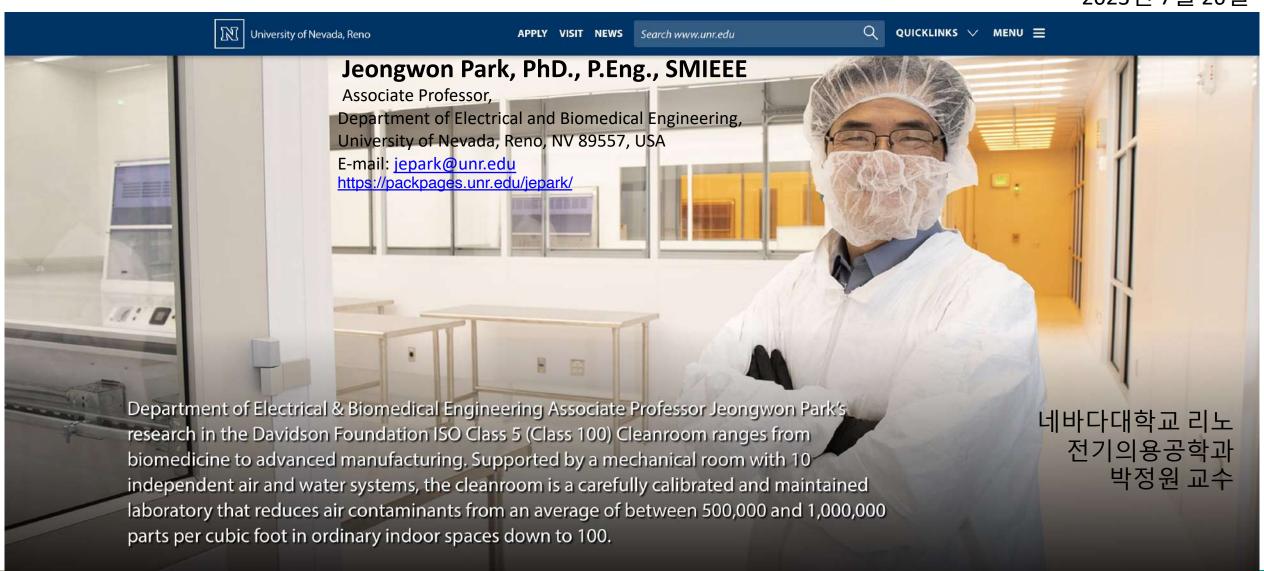

#### Jeongwon Park, PhD.

Associate Professor,

Department of Electrical and Biomedical Engineering,

University of Nevada, Reno, NV 89557, USA

E-mail: jepark@unr.edu

# About the University of Nevada, Reno (UNR)

**21,000+ students**

University of Nevada, Reno

Founded in 1874

1,049 academic faculty

19:1 student-tofaculty ratio

YOLE

#### Jeongwon Park, PhD., P.Eng

Associate Professor.

Department of Electrical and Biomedical Engineering,

E-mail: jepark@unr.edu Cell: 1 (775) 225-6726

## University of Nevada, Reno, NV 89557, USA Research Areas: E-mail: jepark@unr.edu

#### University of Nevada, Reno

# Materials, Sensors and Devices

@2015 | www.yole.fr

NbSe,, etc.

Md. Sherajul Islam 👊 Shahrukh Sadman, A. E. M. Jannatul Islam 🔍 and Jeongwen Park 🕛

Personal care

FIGURE 1 GaN HEMT equivalent circuit-small signal model (EC-SSM) including the substrate-buffer model19

Intrinsic FET

$R_d$   $L_d$  D

# Agenda

- Introduction

- Semiconductor Market and R&D Trends

- Transistor Scaling

- Challenges and Prospects

| Funding details of CHIPS and Science Act (USD).       |                         |                        |  |  |  |

|-------------------------------------------------------|-------------------------|------------------------|--|--|--|

| Key Programs                                          | Five-Year Authorization | Increase over Baseline |  |  |  |

| National Science Foundation (NSF)                     | \$81 billion            | \$36 billion           |  |  |  |

| NSF Tech Directorate                                  | \$20 billion            | \$20 billion           |  |  |  |

| NSF Core activities                                   | \$61 billion            | \$16 billion           |  |  |  |

| Department of Commerce (DOC)                          | \$11 billion            | \$11 billion           |  |  |  |

| Regional Technology Hubs                              | \$10 billion            | \$10 billion           |  |  |  |

| RECOMPETE pilot                                       | \$ 1 billion            | \$ 1 billion           |  |  |  |

| National Institute of Standards and Technology (NIST) | \$10 billion            | \$ 5 billion           |  |  |  |

| NIST research                                         | \$6.9 billion           | \$2.8 billion          |  |  |  |

| Manufacturing USA                                     | \$829 million           | \$744 million          |  |  |  |

| Manufacturing Extension Partnership                   | \$2.3 billion           | \$1.5 billion          |  |  |  |

| Department of Energy (DOE)*                           | \$67.9 billion          | \$30.5 billion         |  |  |  |

| DOE Office of Science                                 | \$50.3 billion          | \$12.9 billion         |  |  |  |

| Additional DOE Science and Innovation                 | \$17.6 billion          | \$17.6 billion         |  |  |  |

| Total                                                 | \$169.9 billion         | \$82.5 billion         |  |  |  |

<sup>\*</sup>Across all the DOE sections, there is:

- A total of \$14.7 billion for infrastructure, equipment, and instrumentation across 17 DOE National Laboratories.

- A total of \$16.5 billion in new or above baseline authorizations for research in the 10 technology areas identified in the United States Innovation and Competition Act of 2021 across the Office of Science and DOE's applied R&D offices in advanced energy and industrial efficiency technologies, artificial intelligence and machine learning, advanced manufacturing, cybersecurity, biotechnology, high performance computing, advanced materials, and quantum information science.

Source: H.R. 4346, The CHIPS and Science Act of 2022, http://www.commerce.senate.gov.

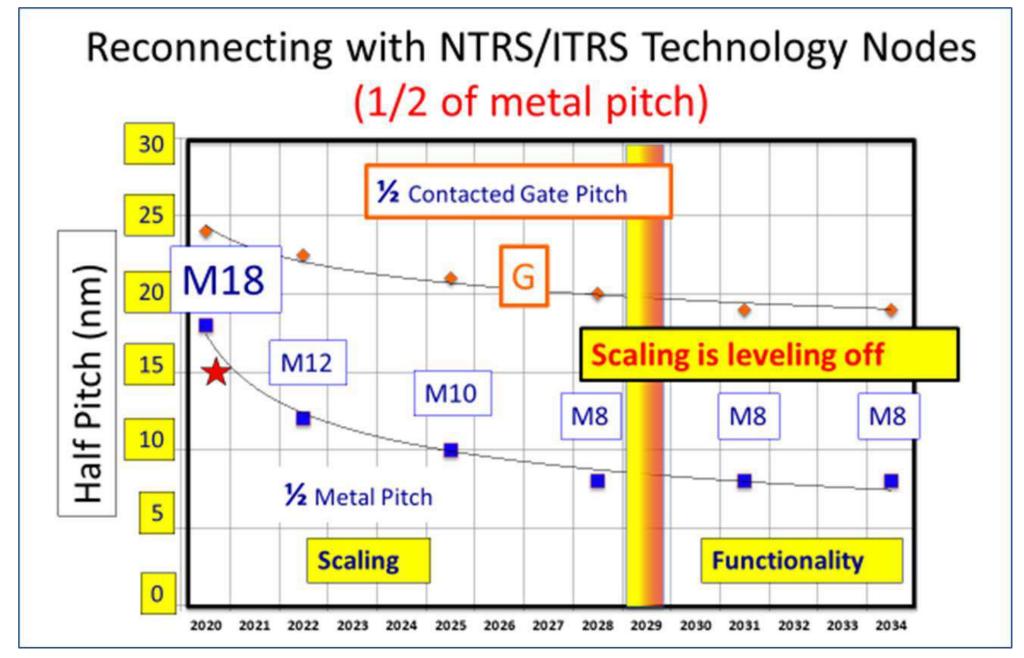

Plateau will be reached:

less than 2 years

2 to 5 years

5 to 10 years

🛕 More than 10 years

Obsolete before plateau

Source: Gartner

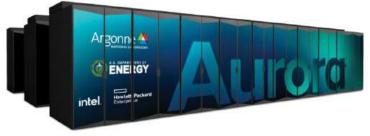

# What is Exascale and Why Zettascale

Performance (FP64-tensor)

> 1 Exaflop

Performance (FP32 -tensor)

> 1 Exaflop

Peak Performance (BF16/Int8 -tensor)

> 8-16 Exaflop

Power

20-30 MW/Exaflop

Goal: Solve fundamental problems from first principles

Zettascale technologies will make Exascale mainstream

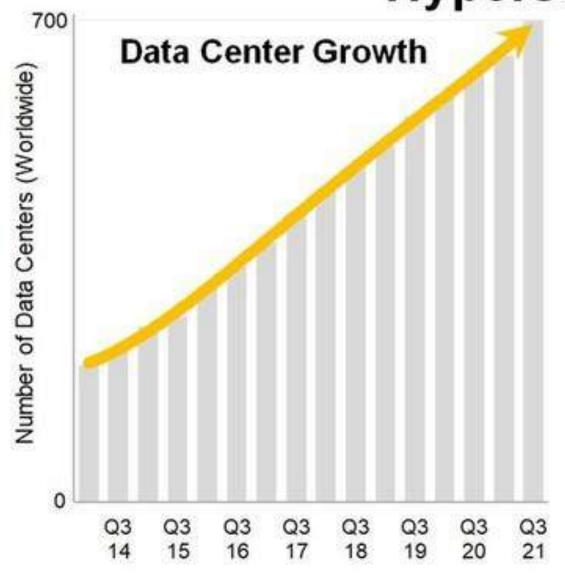

# **Hyperscale Data Centers**

Source: Synergy Research Group

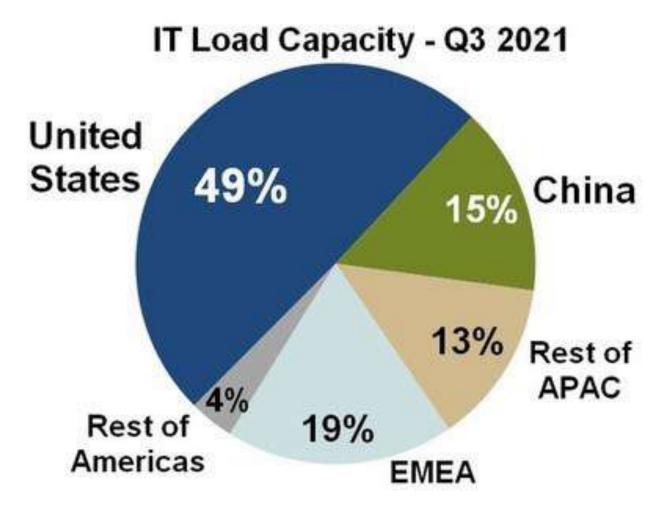

Traffic within data center is main limiting factor

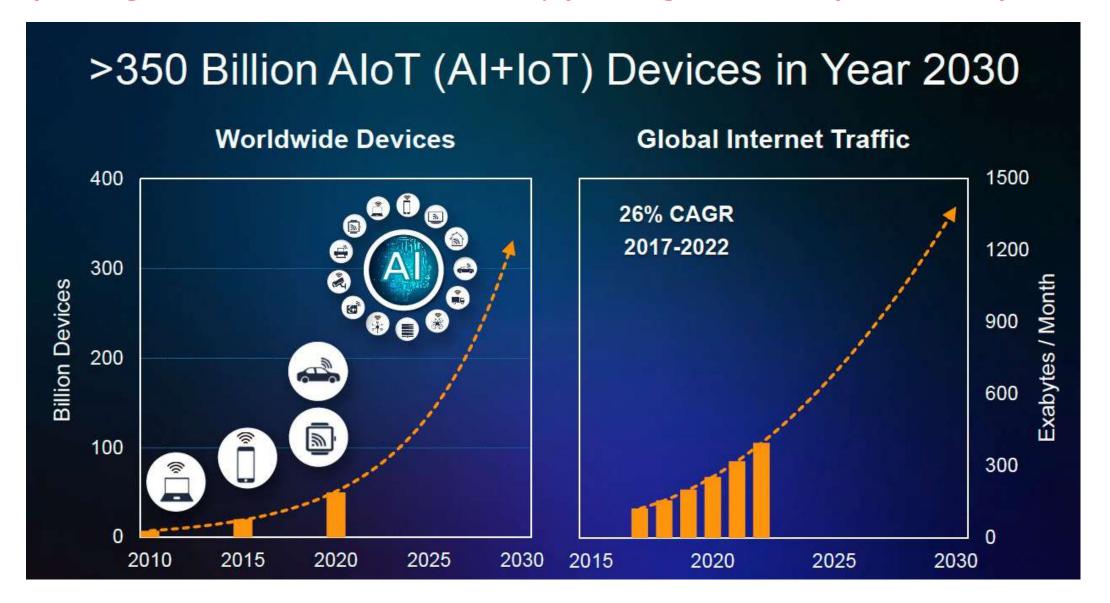

#### Demand for higher data rates concurrently fueling demand of billions of devices

Source: 2020 IEEE ISSCC, Cisco VNI Global IP Traffic Forecast 2017-2022

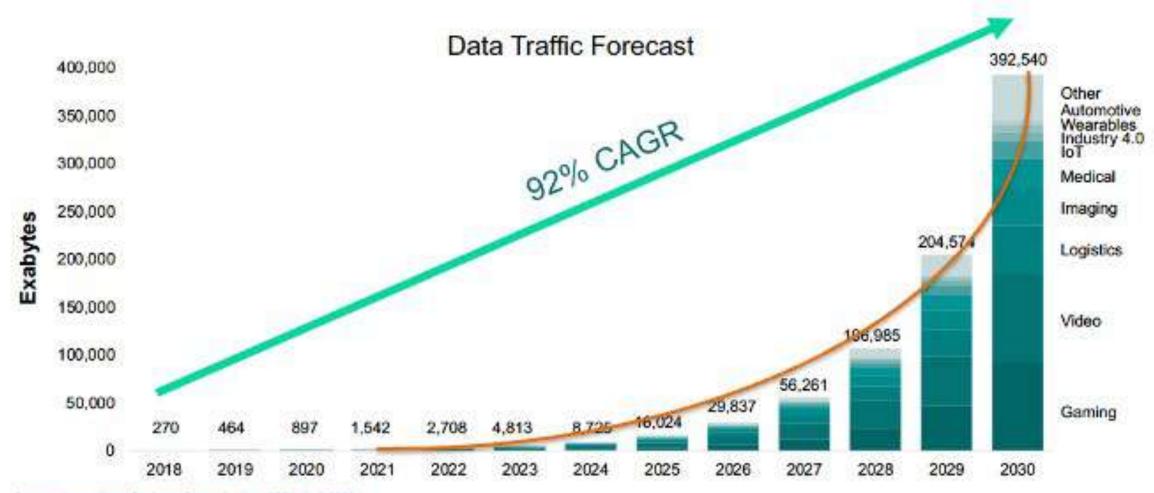

# Exponential data traffic, enabled by machine-to-machine communication

Source: International Business Strategies, Inc. (IBS), April 2020

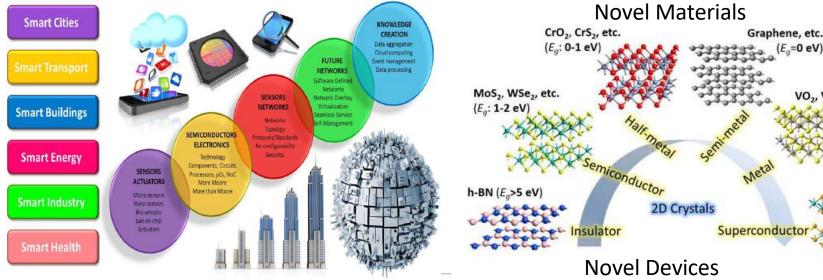

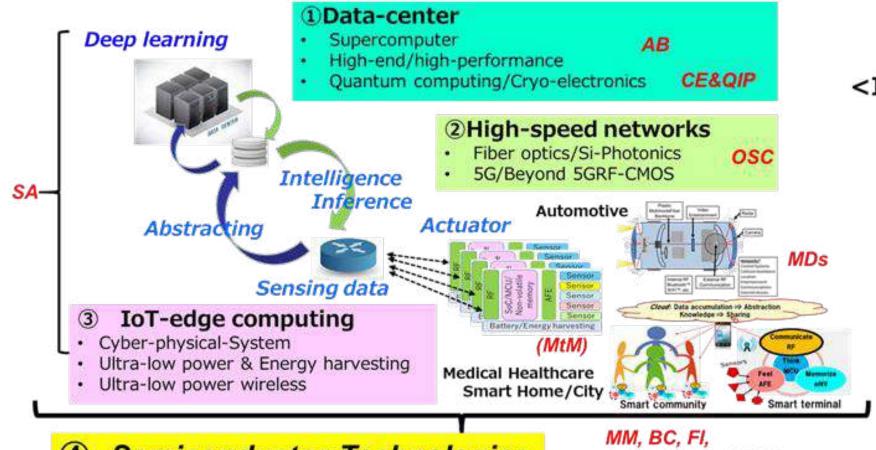

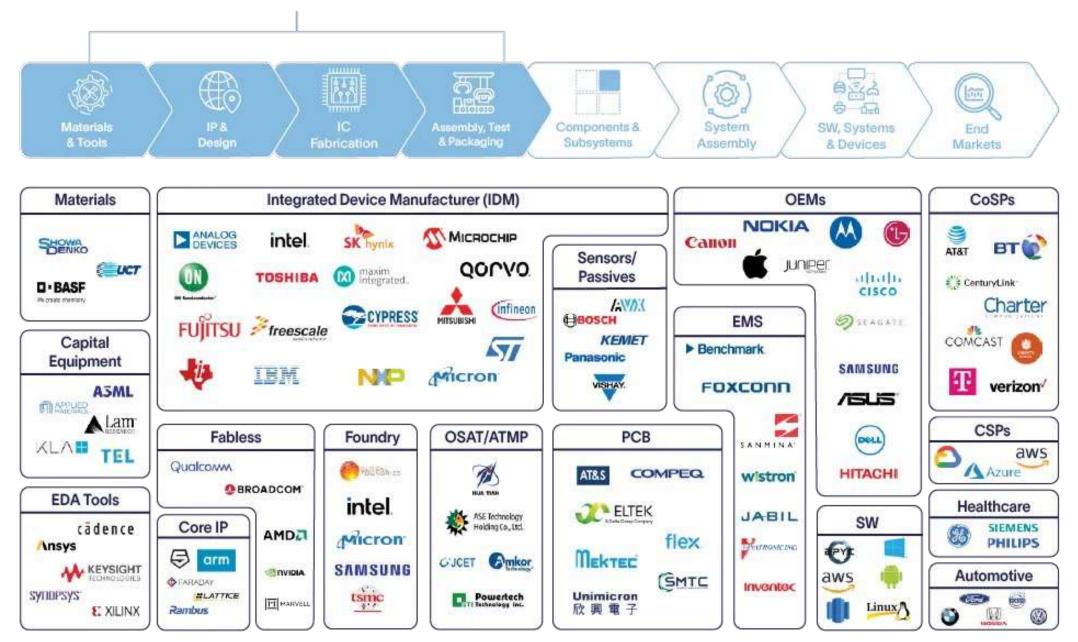

#### The new ecosystem of the electronics' industry based on semiconductor technologies.

<International Collaboration>

International **Roadmap Committee** (IRC@2020.6)

- IEEE IRDS™

- SDRJ/JSAP\*1

- SINANO\*2 institute

Semiconductor Technologies

L, YE, M, PI, ESH/S

AB: Applications Benchmarking, SA: Systems and Architecture, OSC: Outside system Connectivity, MM: More Moore, BC: Beyond CMOS, CE&QIP: Cryogenics Electronics and Quantum Information Processing, PI: Packaging Integration, FI: Factory Integration, L: Lithography, YE: Yield Enhancement, M: Metrology, ESH/S: Environment, Safety, Health, and Sustainability, MtM: More than Moore, MDs: Market drivers (automobile, medical devices).

\*1: The System Device Roadmap Committee of Japan/The Japan Society of Applied Physics \*2: The European Academic and Scientific Association for Nanoelectronics

Semiconductor Clean and Efficient Energy **Semiconductor Applications** Materials **Technologies Areas Power Electronics Solar Cells** for Renewable **Energy Grid** Conventional, thin film, Photovoltaic and perovskite PVs Power Semiconductors Electronics Power electronics for electric transport **Electronic Appliances** (computers, consumer and government tools) Power electronics Wide Bandgap for electrified Other Renewable industry Semiconductors Automotive **Energy Technologies** (SiC, GaN) **Efficient** Industrial computing **Electronics Electric Vehicles** Industrial Electrified Building electronics for Industry Conventional energy efficiency **Electronics** (sensors, controls, Semiconductors machine learning) Building electronics for energy efficiency Communication (lighting sensors, controls, **Detailed supply** Broad Scope of Study: machine learning) chain study Semiconductors for Clean Energy & EE Semiconductor, Supply Chain Deep Dive Assessment, U.S. Department of Energy Response to Executive Order 14017, "America's Supply Chains", February 24, 2022

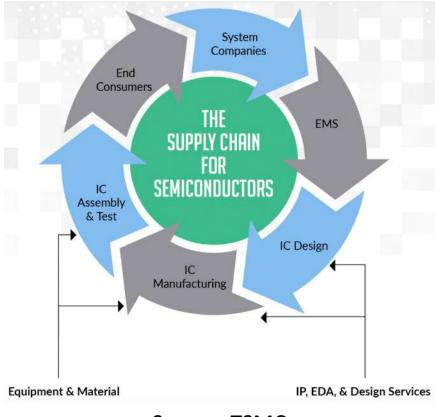

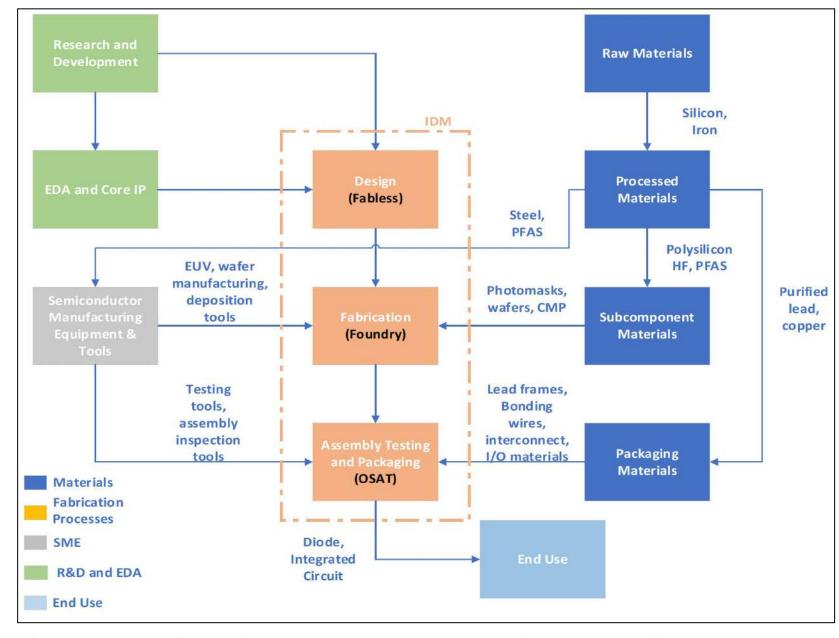

#### Semiconductor Value Chain

Source: TSMC

**Semiconductor**, Supply Chain Deep Dive Assessment, U.S. Department of Energy Response to Executive Order 14017, "America's Supply Chains", February 24, 2022

#### Semiconductor Value Chain

## **Ecosystem of semiconductors**

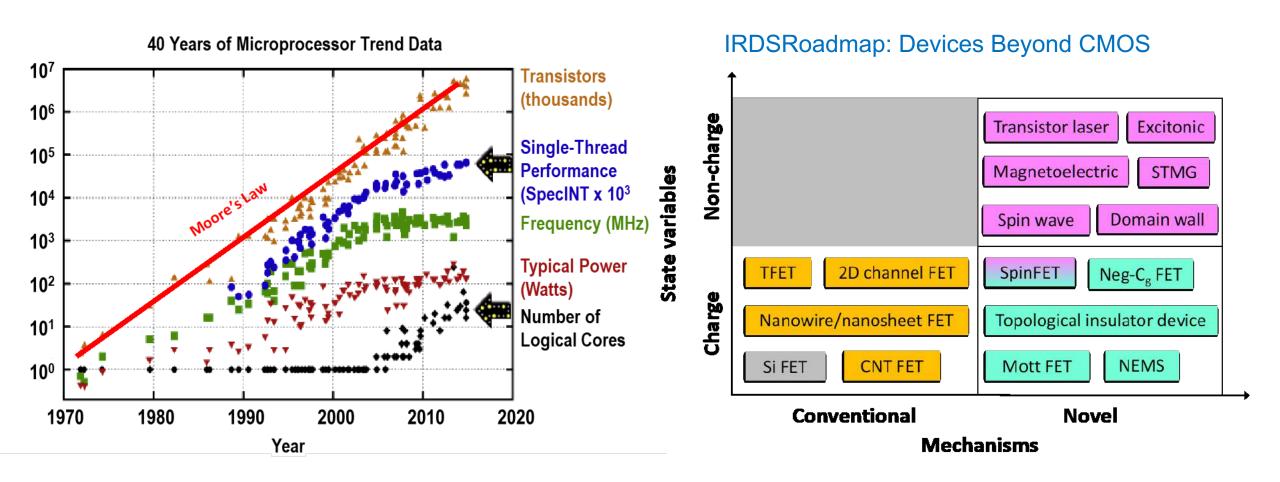

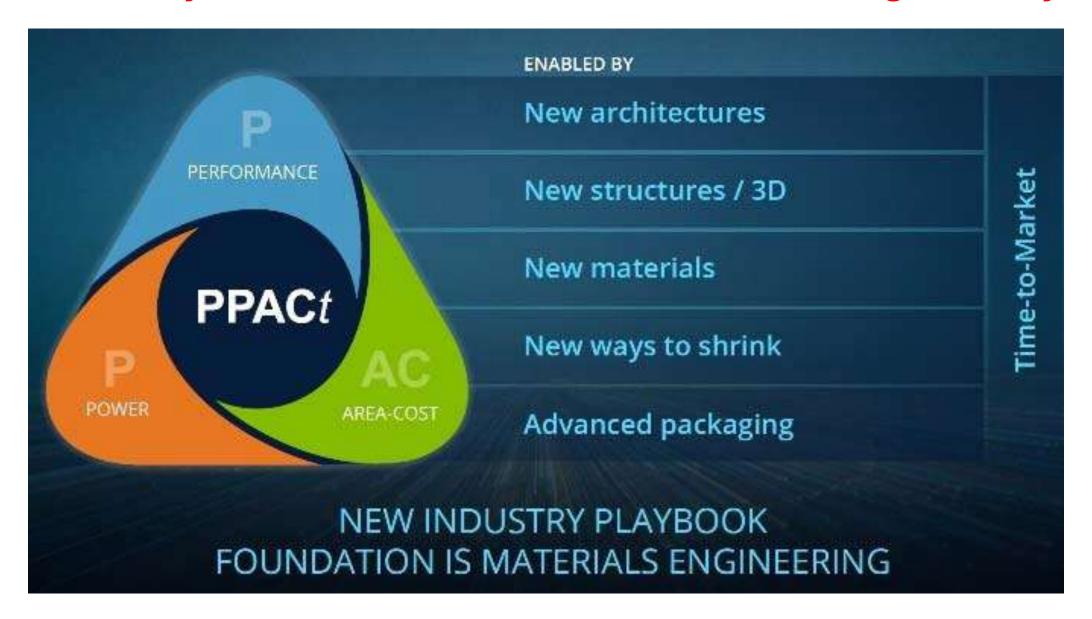

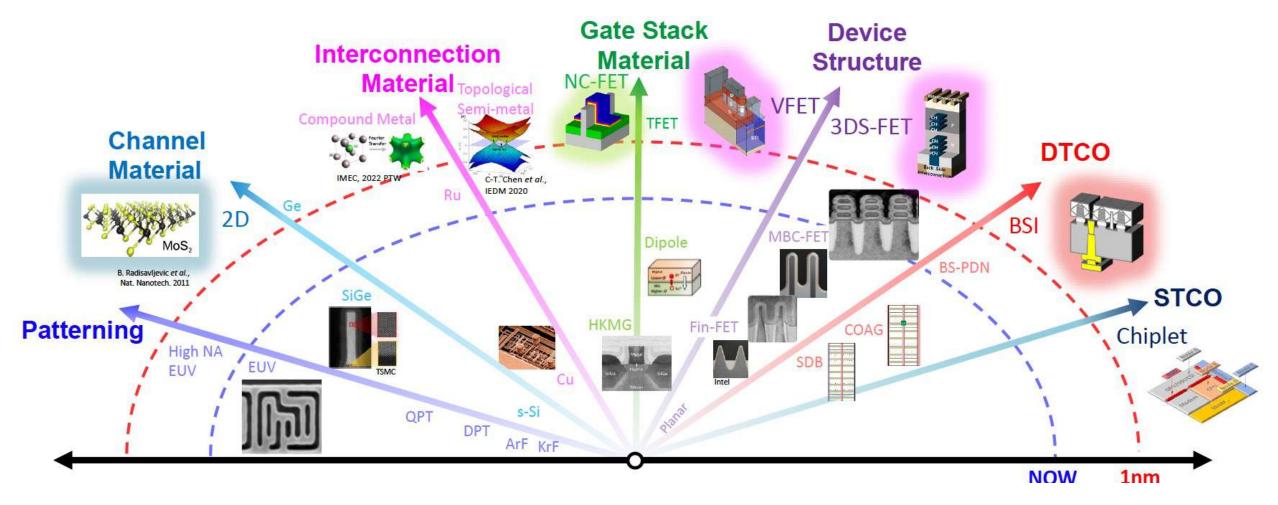

## Nanodevices for Computing and Logic Beyond CMOS

Identify and Mature Options for Semiconductors Beyond the Present State of the Art

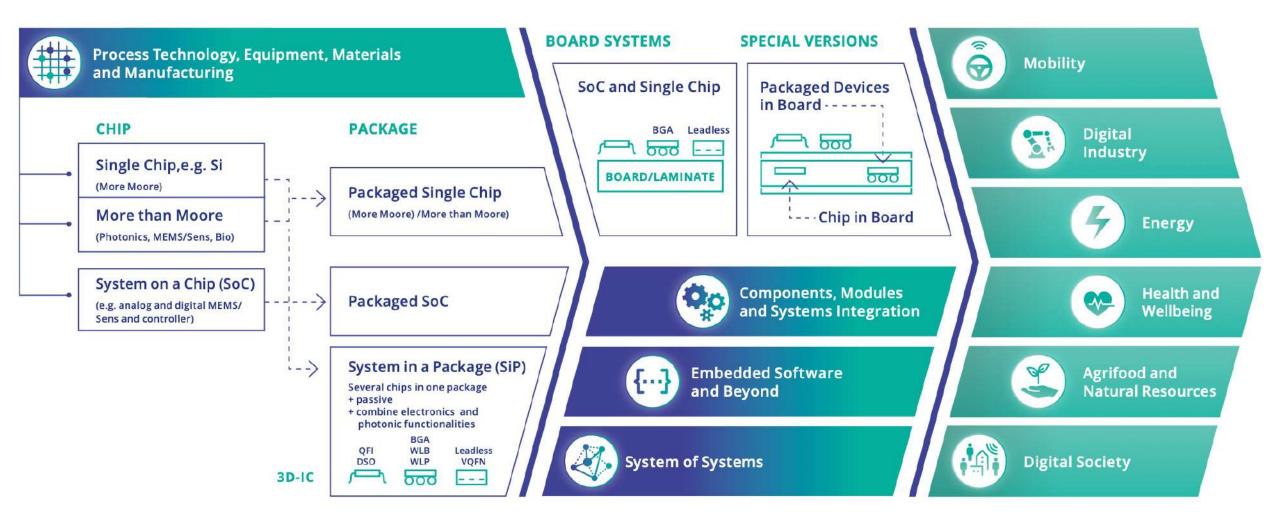

### Materials to Systems in Semiconductor Manufacturing and Beyond

### **Semiconductor Manufacturing**

| New architectures /<br>New devices | CMOS image sensors                | Silicon Seri Wosert Wosert Entr | MRAM                       | Analog compute-in-memory       |

|------------------------------------|-----------------------------------|---------------------------------|----------------------------|--------------------------------|

| New structures / 3D                | 3D NAND                           | 3D GAA Logic                    | 3D DRAM                    | Buried /backside<br>power Rail |

| New materials                      | Low R wining<br>for Logic         | HKMG for<br>DRAM periphery      | Low R contact<br>for Logic | Low it metals for DRAM         |

| New ways to shrink                 | New hard mask +<br>hard mask open | Multi-patterning                | EUV                        | Self-alignment                 |

| Advanced packaging                 | HBM DRAM                          | CMOS bonded<br>attay NAND       | 2.50 logic                 | Logic chiplets                 |

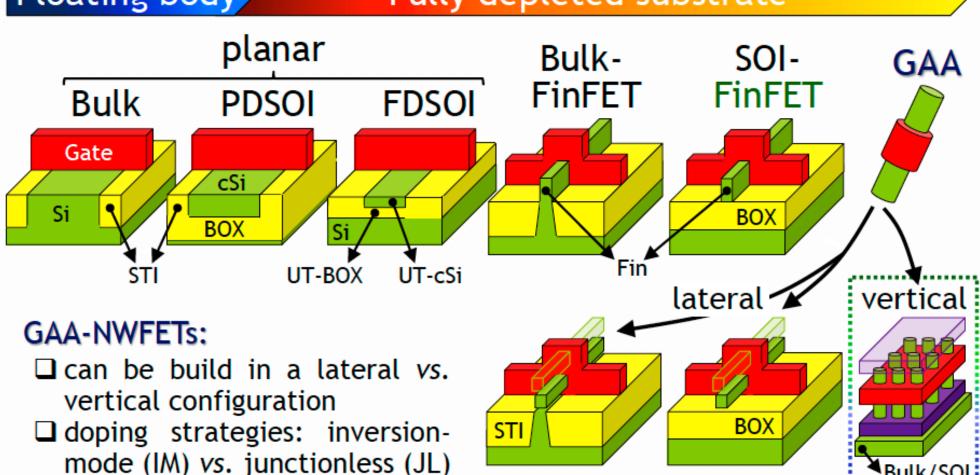

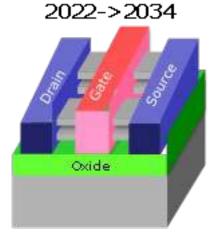

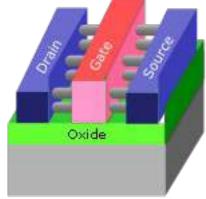

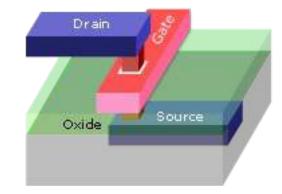

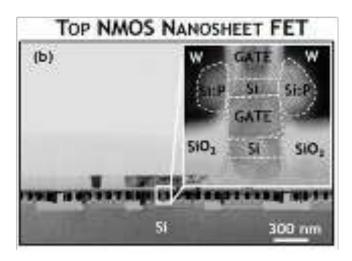

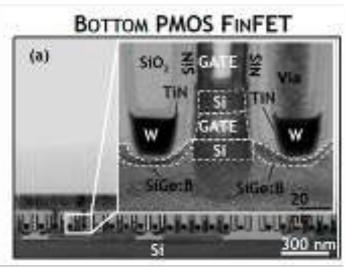

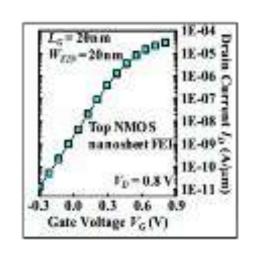

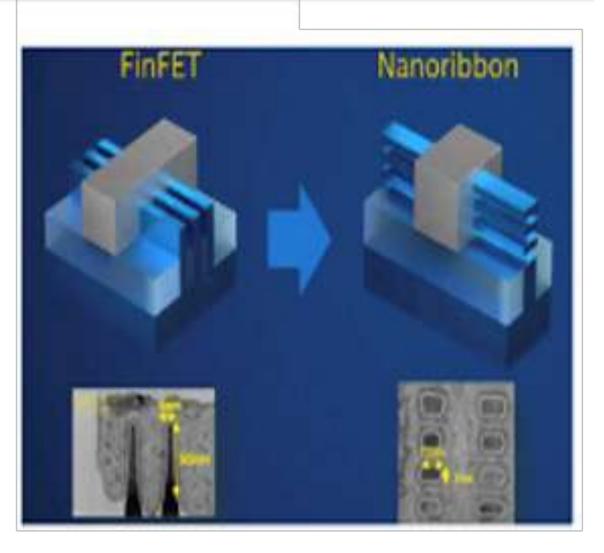

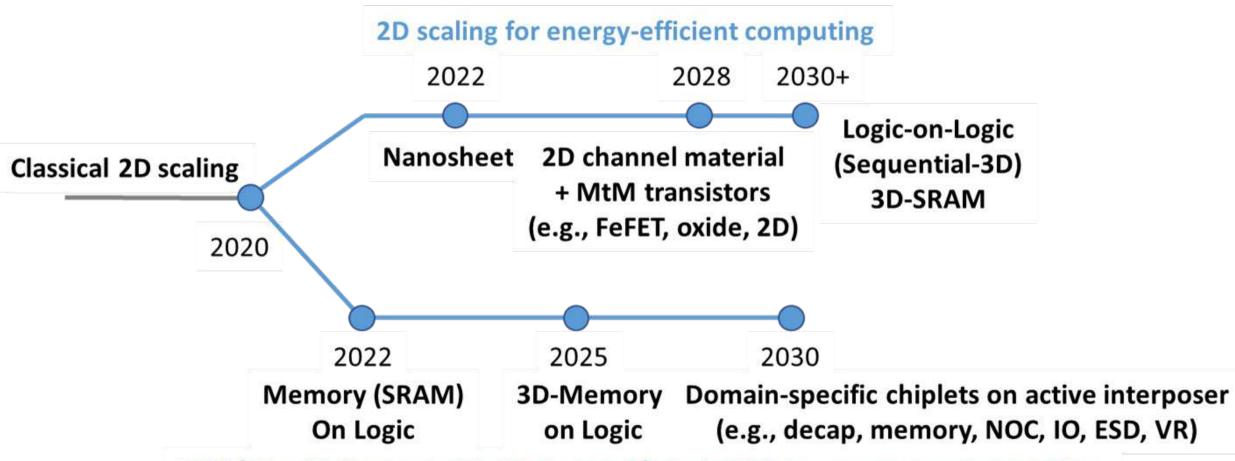

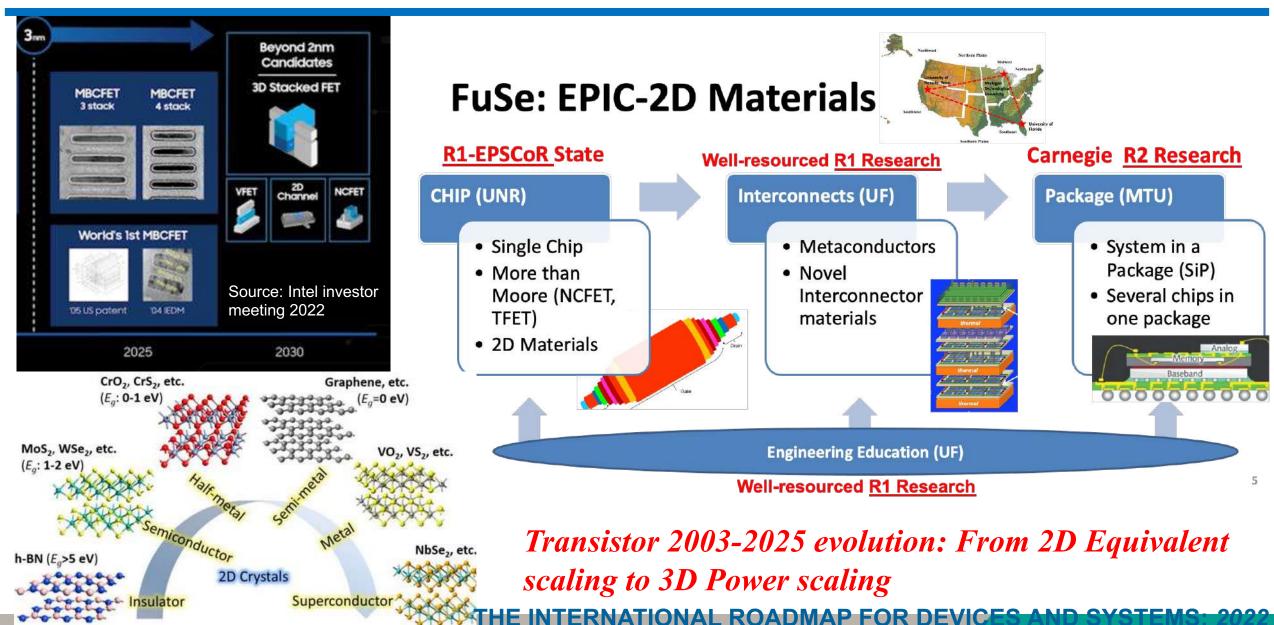

# Introduction: scaling scenario for device architectures

———— scalability, density↑

### Floating body

#### Fully depleted substrate

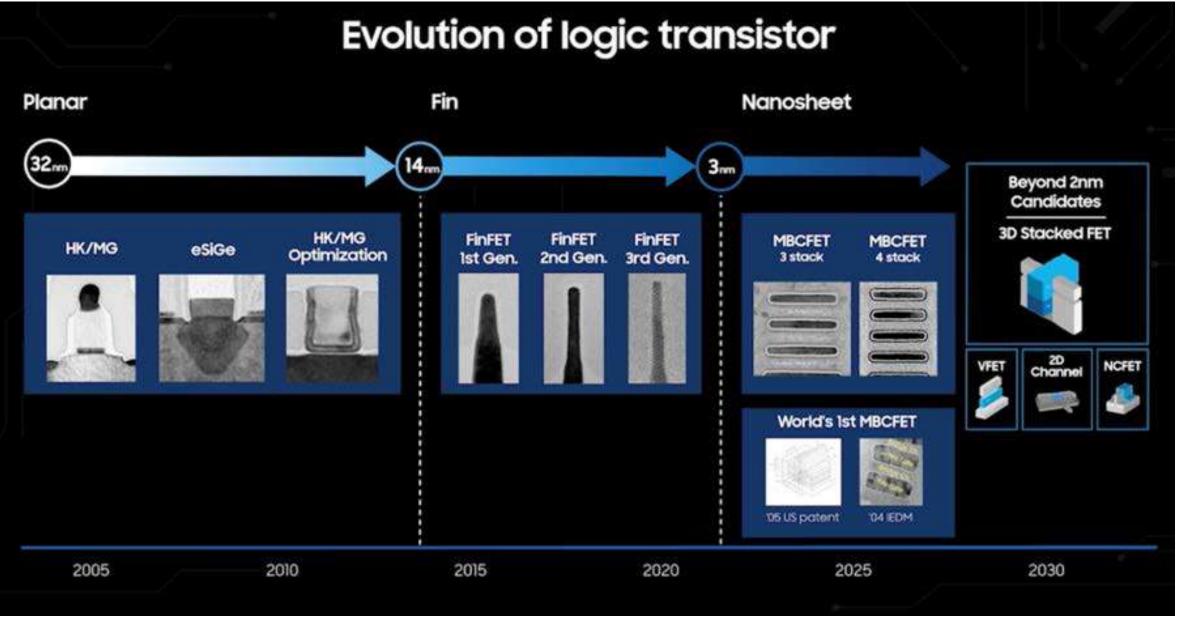

Transistor 2003-2025 evolution: From 2D Equivalent scaling to 3D Power scaling

Source: Intel investor meeting 2022

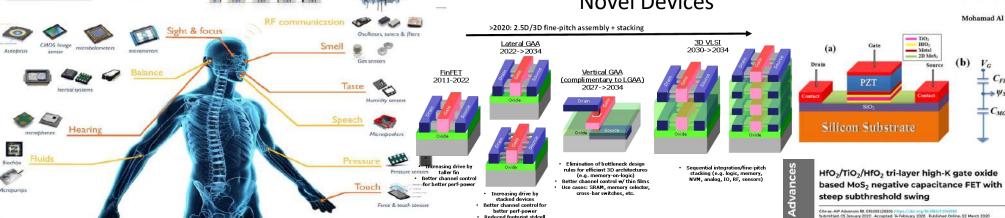

#### >2020: 2.5D/3D fine-pitch assembly + stacking

<u>FinFET</u> 2011-2022

- Increasing drive by taller fin

- Better channel control for better perf-power

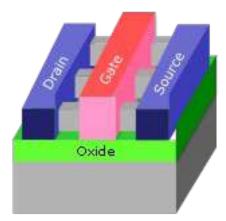

Lateral GAA

- Increasing drive by stacked devices

- Better channel control for better perf-power

- Reduced footprint stdcell

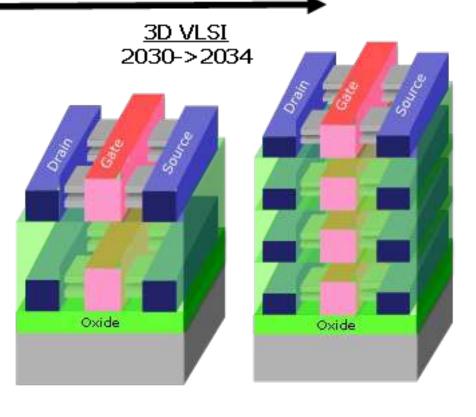

Vertical GAA (complimentary to LGAA) 2027->2034

- Elimination of bottleneck design rules for efficient 3D architectures (e.g. memory-on-logic)

- · Better channel control w/ thin films

- Use cases: SRAM, memory selector, cross-bar switches, etc.

Sequential integration/fine-pitch stacking (e.g. logic, memory, NVM, analog, IO, RF, sensors)

#### Vertical transistors and nanoribbons are progressively entering the logic technology arsenal

Source: IMEC and Intel

| YEAR OF PRODUCTION                                    | 2022      | 2025                                    | 2028              | 2031                    | 2034                    | 2037                    |

|-------------------------------------------------------|-----------|-----------------------------------------|-------------------|-------------------------|-------------------------|-------------------------|

|                                                       | G48M24    | G45M20                                  | G42M16            | G40M16 T2               | G38M16 T4               | G38M16 T6               |

| Logic industry "Node Range" Labeling                  | "3nm"     | "2nm"                                   | "4.5nm"           | "4.0nm eq"              | "0.7nm eq"              | "0.5nm eq"              |

| Fine-pitch 3D integration scheme                      | Stacking  | Stacking                                | Stacking          | 3DVLSI                  | 3DVLSI                  | 3DVLSI                  |

|                                                       | finFET    | 440000000000000000000000000000000000000 | LGAA              | LGAA-3D                 | LGAA-3D                 | LGAA-3D                 |

| Logic device structure options                        | LGAA      | LGAA                                    | CFET-SRAM         | CFET-SRAM               | CFET-SRAM               | CFET-SRAM               |

| Platform device for logic                             | finFET    | LGAA                                    | LGAA<br>CFET-SRAM | LGAA-3D<br>CFET-SRAM-3D | LGAA-3D<br>CFET-SRAM-3D | LGAA-3D<br>CFET-SRAM-3D |

|                                                       | 0.624     |                                         | Oxide<br>Oxide    | tier tier tier tier     | tier tier tier tier     | Cype tier tier tier     |

| LOGIC DEVICE GROUND RULES                             |           |                                         |                   |                         |                         |                         |

| Mx pitch (nm)                                         | 32        | 24                                      | 20                | 16                      | 16                      | 16                      |

| M1 pRch (nm)                                          | 32        | 23                                      | 21                | 28                      | 19                      | 19                      |

| MO pitch (nm)                                         | 24        | 20                                      | 16                | 16                      | 16                      | 16                      |

| Gate pitch (nm)                                       | 48        | 45                                      | 42                | 40                      | 38                      | 38                      |

| Lg: Gate Length - HP (nm)                             | 16        | 14                                      | 12                | 12                      | 12                      | 12                      |

| Lg: Gate Length - HD (nm)                             | 18        | 14                                      | 12                | 12                      | 12                      | 12                      |

| Channel overlap ratio - two-sided                     | 8.28      | 0.20                                    | 0.20              | 0.20                    | 0.20                    | 0.20                    |

| Spacer width (nm)                                     | 6         | 6                                       | 5                 | 6                       | 4                       |                         |

| Spacer k value                                        | 3.5       | 3.3                                     | 3.0               | 3.0                     | 2.7                     | 2.7                     |

| Contact CD (nm) - finFET, LGAA                        | 20        | 19                                      | 20                | 18                      | 18                      | 18                      |

| Device architecture key ground rules                  |           |                                         | 150               |                         |                         |                         |

| Device lateral pitch (nm)                             | 24        | 26                                      | 24                | 24                      | 23                      | 23                      |

| Device height (nm)                                    | 48        | 52                                      | 48                | 64                      | 60                      | 56                      |

| FinFET Fin width (nm)                                 | 5.0       | 32                                      | 40                | 04                      | 00                      | 30                      |

| Footprint drive efficiency - finFET                   | 4.21      |                                         |                   |                         |                         |                         |

|                                                       | 4.21      | 40.0                                    | 40.0              | 40.0                    | 46.6                    | 444                     |

| Lateral GAA vertical pitch (nm)                       |           | 18.0                                    | 16.0              | 16.0                    | 15.0                    | 14.0                    |

| Lateral GAA (nanosheet) thickness (nm)                |           | 6.0                                     | 6.0               | 6.0                     | 5.0                     | 4.0                     |

| Number of vertically stacked nanosheets on one device | 2         | 3                                       | 3                 | 4                       | 4                       | 4                       |

| LGAA width (nm) - HP                                  |           | 30                                      | 30                | 20                      | 15                      | 15                      |

| LGAA width (nm) - HD                                  |           | 15                                      | 10                | 10                      | 6                       | 6                       |

| LGAA width (nm) - SRAM                                |           | 7                                       | 6                 | 6                       | 6                       | 6                       |

| Footprint drive efficiency - lateral GAA - HP         | 110000000 | 4.41                                    | 4.50              | 5.47                    | 5.08                    | 4.75                    |

| Device effective width (nm) - HP                      | 101.0     | 216.0                                   | 216.0             | 208.0                   | 160.0                   | 152.0                   |

| Device effective width (nm) - HD                      | 101.0     | 126.0                                   | 96.0              | 128.0                   | 88.0                    | 80.0                    |

| PN seperation width (nm)                              | 45        | 40                                      | 20                | 15                      | 15                      | 18                      |

#### THE INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS: 202

### Overall technology progression in the 2022 IRDS remains close to forecast.

| YEAR OF PRODUCTION                                   | 2021                            | 2022                                     | 2025                                     | 2028                                                                   | 2031                                                            | 2034                                      |

|------------------------------------------------------|---------------------------------|------------------------------------------|------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------|

|                                                      | G51M30                          | G48M24                                   | G45M20                                   | G42M16                                                                 | G40M16/T2                                                       | G38M16/T4                                 |

| Logic industry "Node Range" Labeling (nm)            | "5"                             | "3"                                      | "2.1"                                    | "1.5"                                                                  | "1.0 eq"                                                        | "0.7 eq"                                  |

| IDM-Foundry node labeling                            | i7-f5                           | i5-f3                                    | i3-f2.1                                  | i2.1-f1.5                                                              | i1.5e-f1.0e                                                     | i1.0e-f0.7e                               |

| Logic device structure options                       | FinFET                          | finFET<br>LGAA                           | LGAA                                     | LGAA                                                                   | LGAA-3D                                                         | LGAA-3D                                   |

| Platform device for logic                            | finFET                          | finFET                                   | LGAA                                     | LGAA                                                                   | LGAA-3D                                                         | LGAA-3D                                   |

| Frequency scaling - node-to-node                     | -                               | 0.02                                     | 0.16                                     | 0.09                                                                   | -0.08                                                           | -0.01                                     |

| CPU frequency at constant power density (GHz)        | 3.13                            | 2.83                                     | 3.53                                     | 2.50                                                                   | 1.48                                                            | 0.86                                      |

| Power at iso frequency - node-to-node                | -                               | -0.16                                    | -0.27                                    | -0.05                                                                  | -0.06                                                           | -0.08                                     |

| Power density - relative                             | 1.00                            | 1.12                                     | 1.04                                     | 1.59                                                                   | 2.51                                                            | 4.27                                      |

| LOGIC TECHNOLOGY ANCHORS                             |                                 |                                          |                                          |                                                                        |                                                                 |                                           |

| Patterning technology inflection for Mx interconnect | 193i, EUV DP                    | 193i, EUV DP                             | 193i, EUV DP                             | 193i, High-NA<br>EUV                                                   | 193i, High-NA<br>EUV                                            | 193i, High-NA<br>EUV                      |

| Beyond-CMOS as complimentary to platform CMOS        | -                               | -                                        | -                                        | 2D Device,<br>FeFET                                                    | 2D Device,<br>FeFET                                             | 2D Device,<br>FeFET                       |

| Channel material technology inflection               | SiGe25%                         | SiGe50%                                  | SiGe50%                                  | Ge, 2D Mat                                                             | Ge, 2D Mat                                                      | Ge, 2D Mat                                |

| Process technology inflection                        | Conformal<br>Doping,<br>Contact | Channel, RMG                             | Lateral/AtomicE<br>tch                   | Non-Cu Mx                                                              | 3DVLSI                                                          | 3DVLSI                                    |

| Stacking generation inflection                       | 2D                              | 3D-stacking:<br>W2W, D2W<br>Mem-on-Logic | 3D-stacking:<br>W2W, D2W<br>Mem-on-Logic | 3D-stacking,<br>Fine-pitch<br>stacking, P-over-<br>N, Mem-on-<br>Logic | 3D-stacking,<br>3DVLSI:<br>Mem-on-Logic<br>with<br>Interconnect | 3D-stacking,<br>3DVLSI:<br>Logic-on-Logic |

Devices will continue to aggressively scale in the next 5 years

#### Logic/Foundry Process Roadmaps (for Volume Production)

|                 | 2016  | 2017                        | 2018                   | 2019                     | 2020                 | 2021                        | 2022       |

|-----------------|-------|-----------------------------|------------------------|--------------------------|----------------------|-----------------------------|------------|

| Intel           | 14nm+ | 10nm<br>(limited)<br>14nm++ |                        | 10nm                     | 10nm+                | 10nm++                      | 7nm<br>EUV |

| Samsung         | 10nm  |                             | 8nm                    | 7nm<br>EUV<br>6nm<br>EUV | 18nm<br>FDSOI<br>5nm | 4nm                         | 3nm<br>GAA |

| тѕмс            | 10nm  | 7<br>12nm                   | nm                     | 7nm+<br>EUV              | 5nm<br>6nm           | 5nm+                        | 4nm<br>3nm |

| GlobalFoundries |       |                             | nm 12nm<br>OSOI finFET |                          | 12nm FDSOI F         | nm+<br>DSOI 12nm+<br>finFET |            |

| SMIC            |       |                             |                        | 14nm<br>finFET           | 12nm<br>finFET       |                             | 0nm<br>FET |

| имс             |       | 14nm<br>finFET              |                        |                          | 22nm<br>planar       |                             |            |

Note: What defines a process "generation" and the start of "volume" production varies from company to company, and may be influenced by marketing embelishments, so these points of transition should only be seen as very general guidelines.

Sources: Companies, conference reports and IC Insights

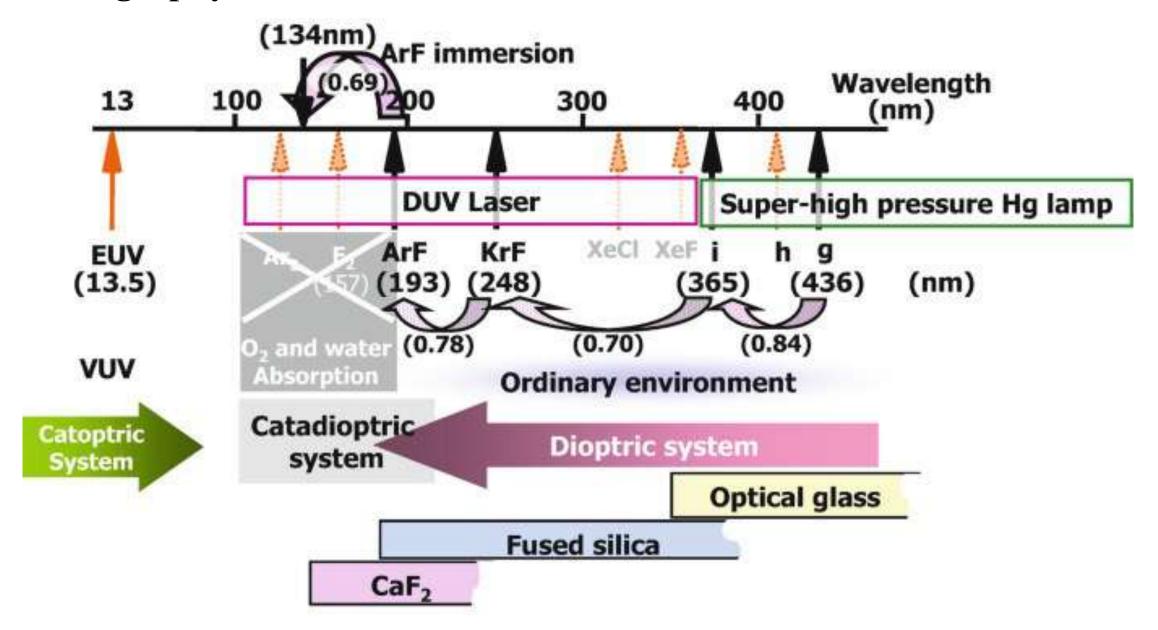

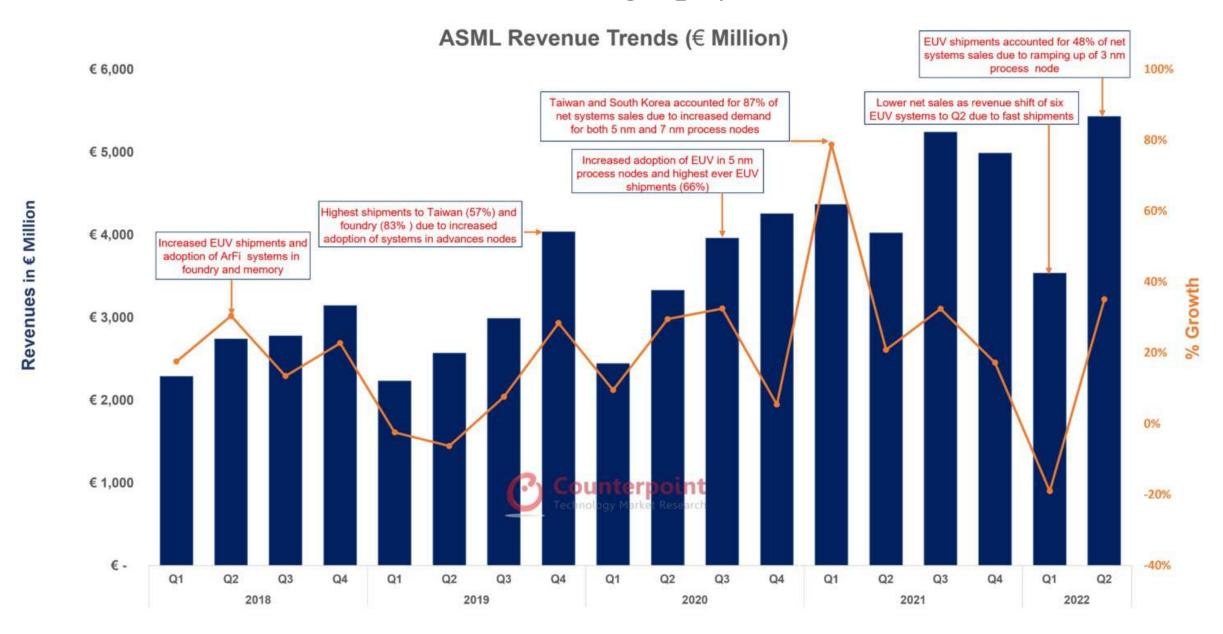

#### Lithography scanners

#### Growth of EUV lithography scanners

# TSMC Advanced Technology Roadmap

https://semiwiki.com/semiconductor-manufacturers/tsmc/328096-tsmc-2023-north-america-technology-symposium-overview-part-1/

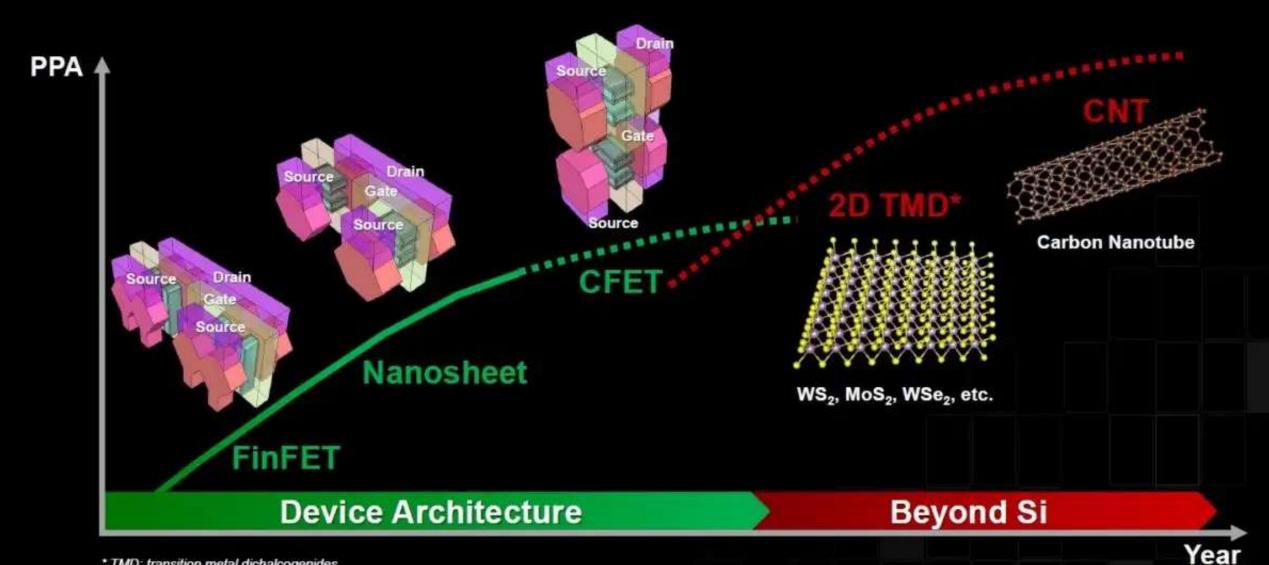

## **Device Architecture Outlook**

<sup>\*</sup> TMD: transition metal dichalcogenides

TSMC Property

https://semiwiki.com/semiconductor-manufacturers/tsmc/328118-tsmc-2023-north-america-technology-symposium-overview-part-2/

# Potential logic scaling roadmap extension

2018 2022 2024 2026 2028 2030 2032 2034 2020 2036 N<sub>2</sub> A10 **A7** A5 **A3** N5 N3 N7 **A14** A2 Metal Continued dimensional scaling Pitch 40 28 21 21 18 18 16 16 16 16-12 (nm) **Device and material innovations** Metal 5 <4T <4T **Tracks FSFET FSFET** GAA GAA **finFET CFET** finFET finFET **CFET**

#### **Context-aware interconnect**

**NSFET**

**NSFET**

CFET

atomic

Sources: Companies, conference reports and IC Insights

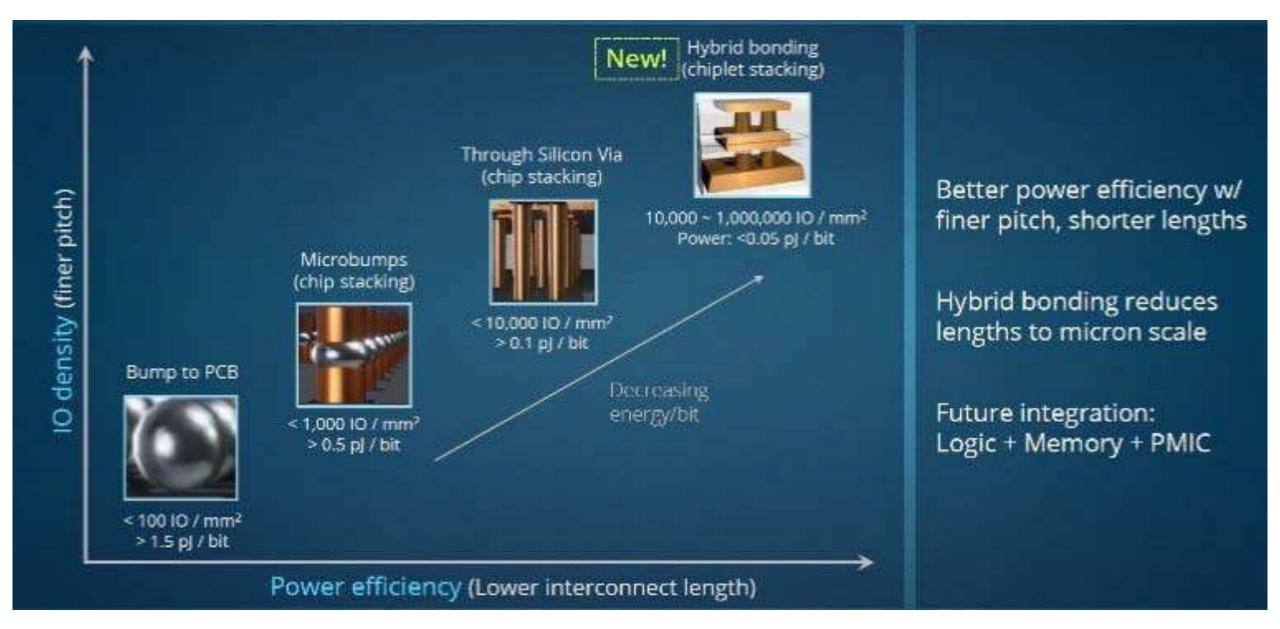

#### System interconnect roadmap of advanced packaging, with hybrid bonding as a new key enabler

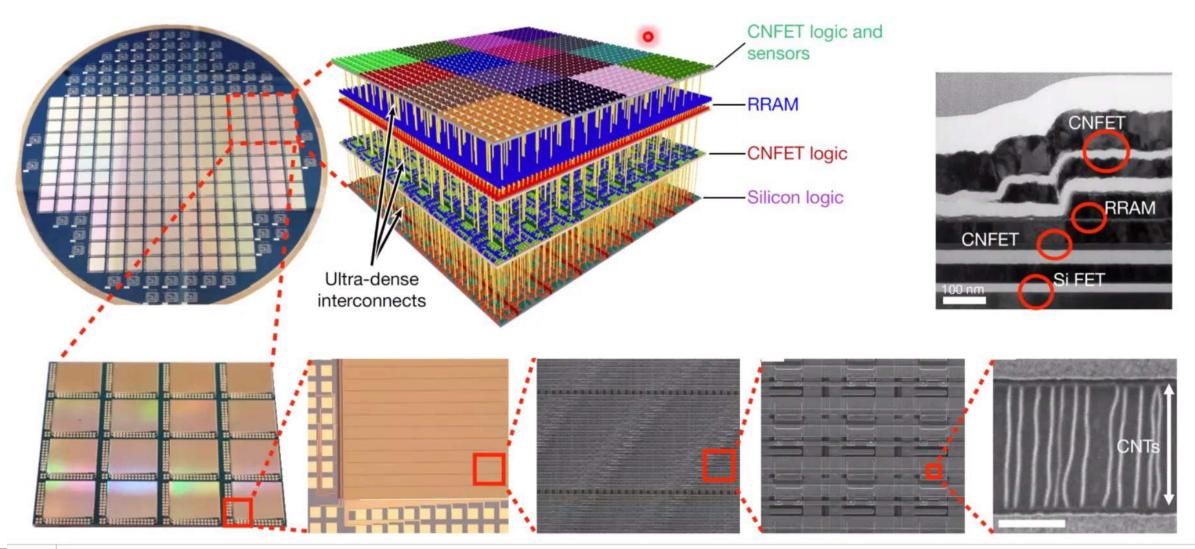

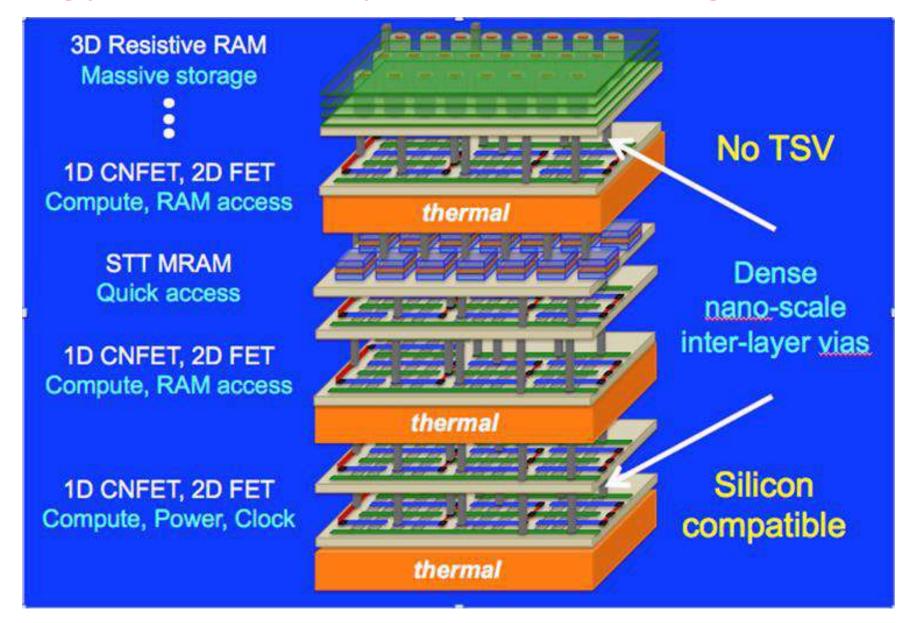

### **N3XT NANOSYSTEM**

> 2 MILLION CNFETS, 1 MBIT RRAM

# Planning for the advent of monolithic heterogeneous integration

## **N3XT CHIP**

# ULT = upper layer transistor

Thermal management

Ultra-dense 3D vertical connectivity (e.g., monolithic Inter-Layer Vias, ILVs)

ULT for memory cells (e.g. Oxide semi. FETs for gain cell memory)

ULT logic for computing (e.g. CNFETs)

ULT for memory access (e.g. 2D FETs)

Dense memory (e.g. 3D-VRRAM)

Si logic (e.g. FinFET)

#

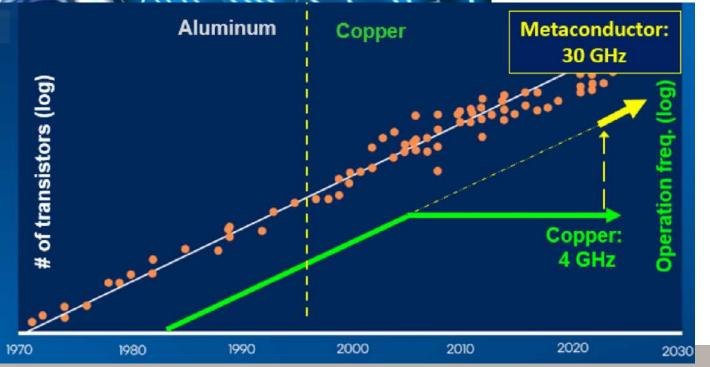

# The Different Ages of Scaling

(Different methods for different times)

### 1 Geometrical Scaling (1975-2002)

Reduction of horizontal and vertical physical dimensions in conjunction with improved performance of planar transistors

#### 2 Equivalent Scaling (2003~2024)

Reduction of only horizontal dimensions in conjunction with introduction of new materials and new physical effects. New vertical structures replace the planar transistor

### 3 3D Power Scaling (2025~2040)

Transition to complete vertical device structures. Heterogeneous integration in conjunction with reduced power consumption become the technology drivers

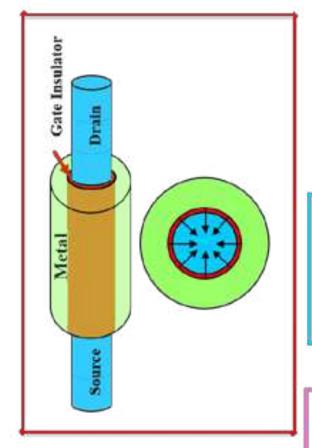

## The Ideal 3D MOS Transistor (2025~2040)

Fully Surrounding Metal Electrode

High-K Gate Insulator

Band Engineered Semiconductor Fully Enclosed, Depleted Semiconductor

Low Resistance Source/Drain

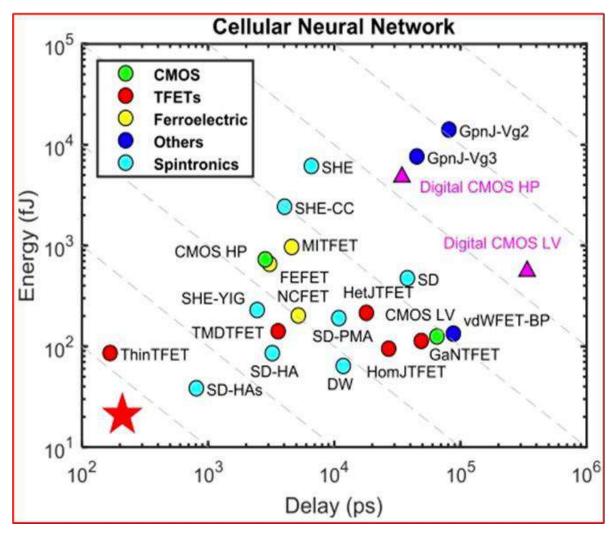

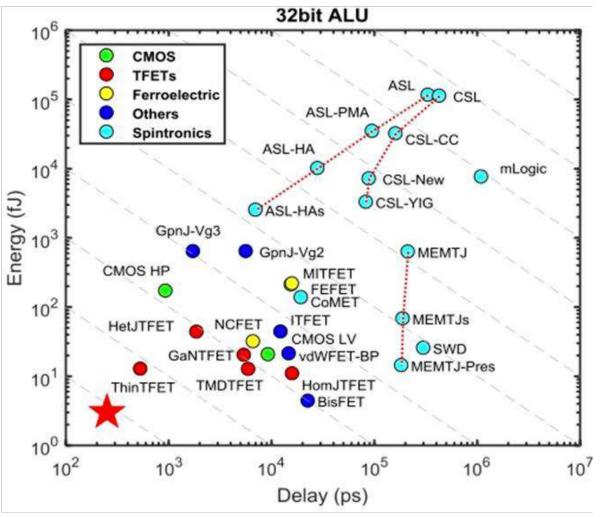

# **TFET Performance is Moving Close to the Target!**

Beyond CMOS continues to improve towards goal!

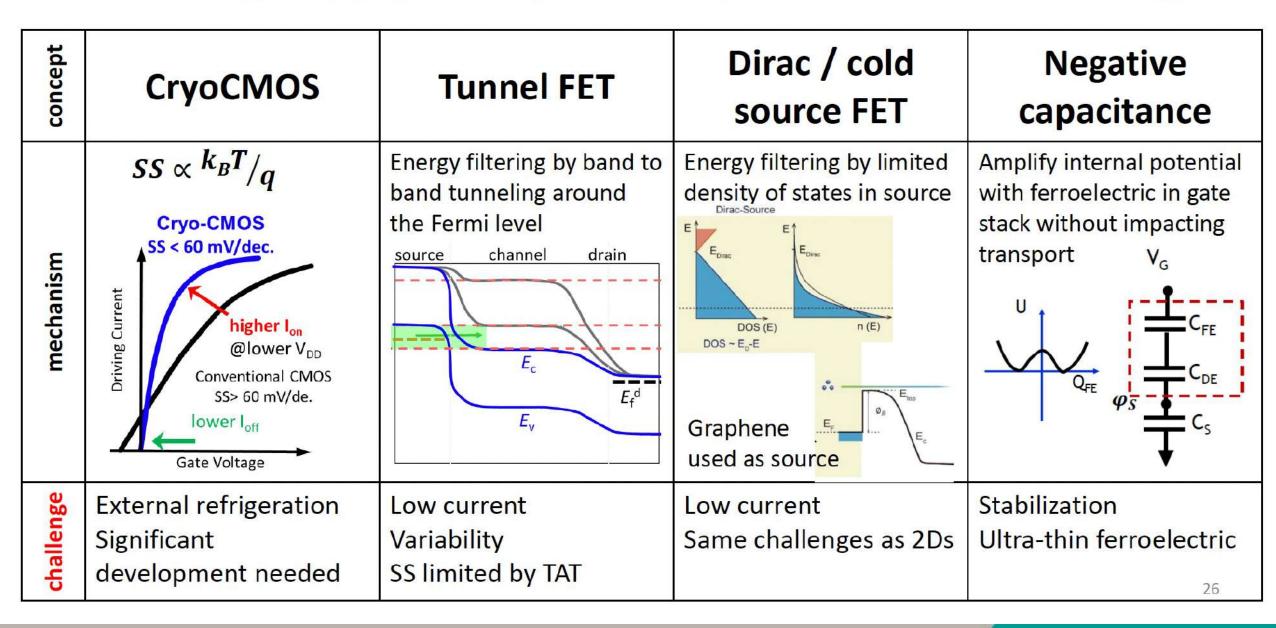

# Reducing supply voltage—Steep subthreshold swing

## 2 complementing routes for More Moore scaling

2.5D/3D+chiplet assembly high-speed/bandwidth bus + memory integration for increased system throughput – TOPS/Watt, TOPS/mm2

# **Candidates for Energy Efficient CMOS Devices**

"Innovations in structures, materials & processes to shrink standard cell area without decreasing effective device width & minimum metal width"

# **Emerging Semiconductor Heterogeneous Integration**

Next-Generation Compound Semiconductor Project (2022-2025)

B5G/6G High Frequency Semiconductor Technologies

GaN and InP compound semiconductor devices and circuits

Wide Bandgap High Power Semiconductor Technologies

GaN, SiC based wide bandgap devices and circuits

- B5G/6G Prospective Technology Developments (2021-2024)

- Sub-THz / THz technology

- Low-Earth Orbit (LEO) communications

- B5G/6G electromagnetic technology

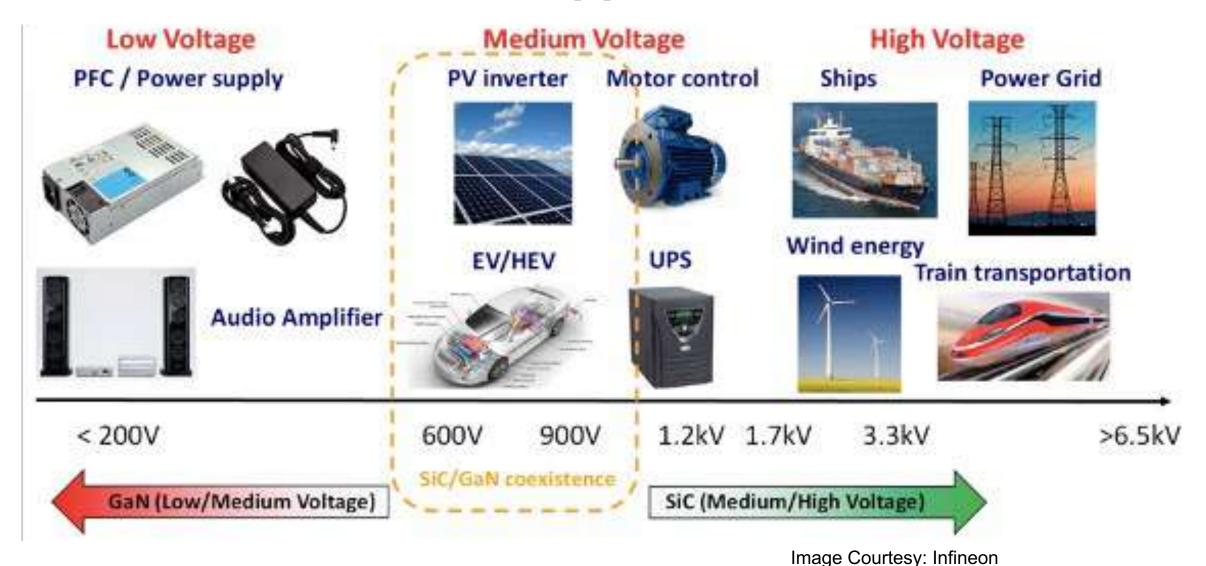

# Wide-Bandgap Semiconductors (SiC, and GaN) for Power Applications

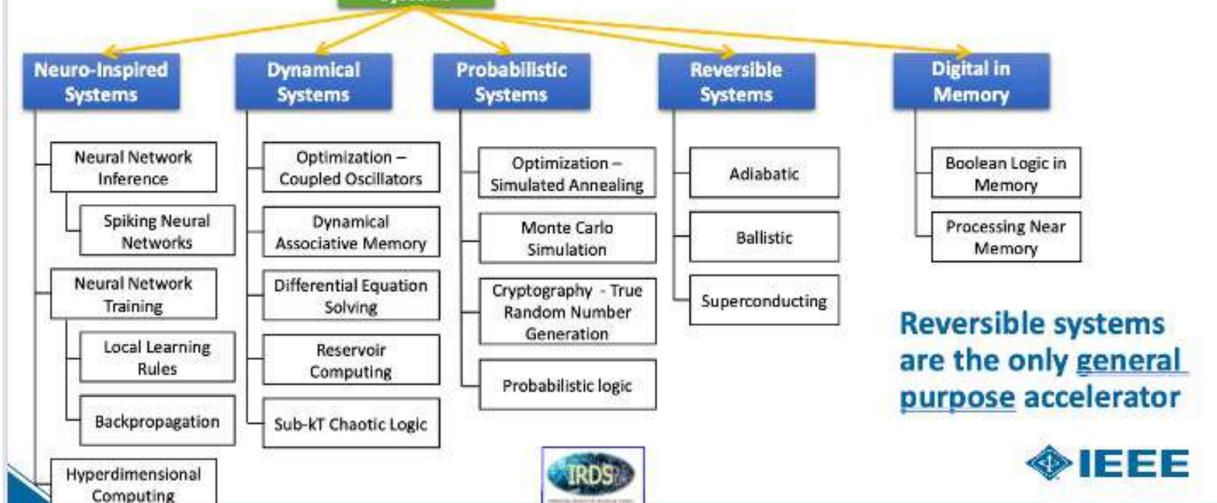

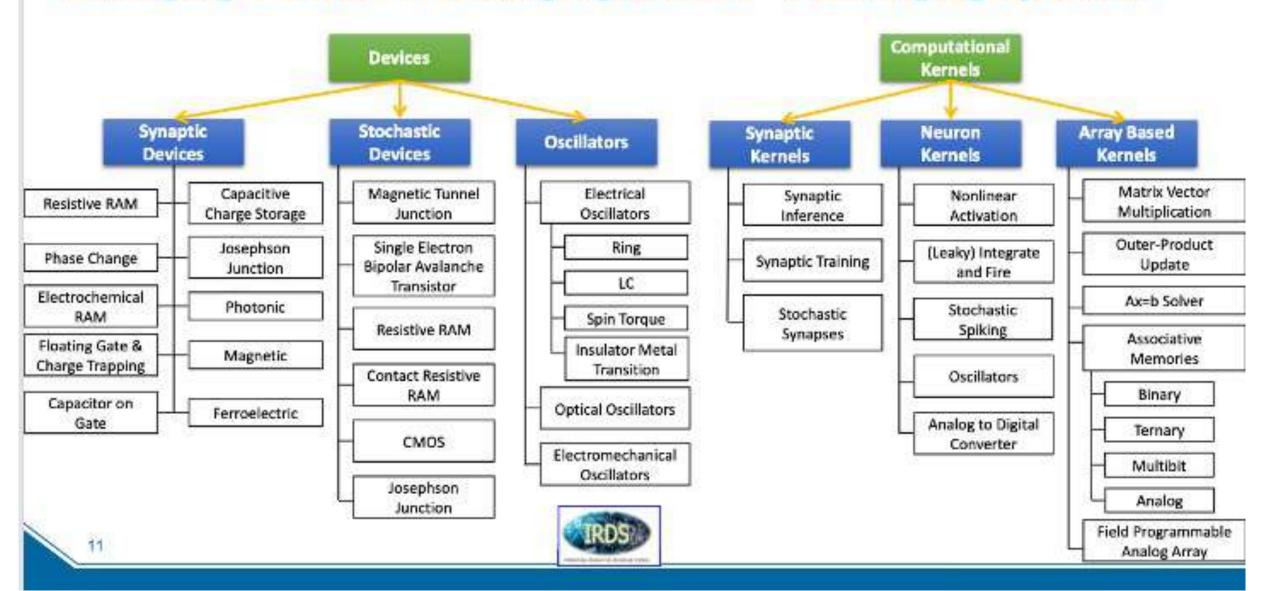

# Most Emerging Systems Accelerate a Particular Class of Problems

Architectures/ Systems

# **Emerging Devices** → **Emerging Kernels** → **Emerging Systems**

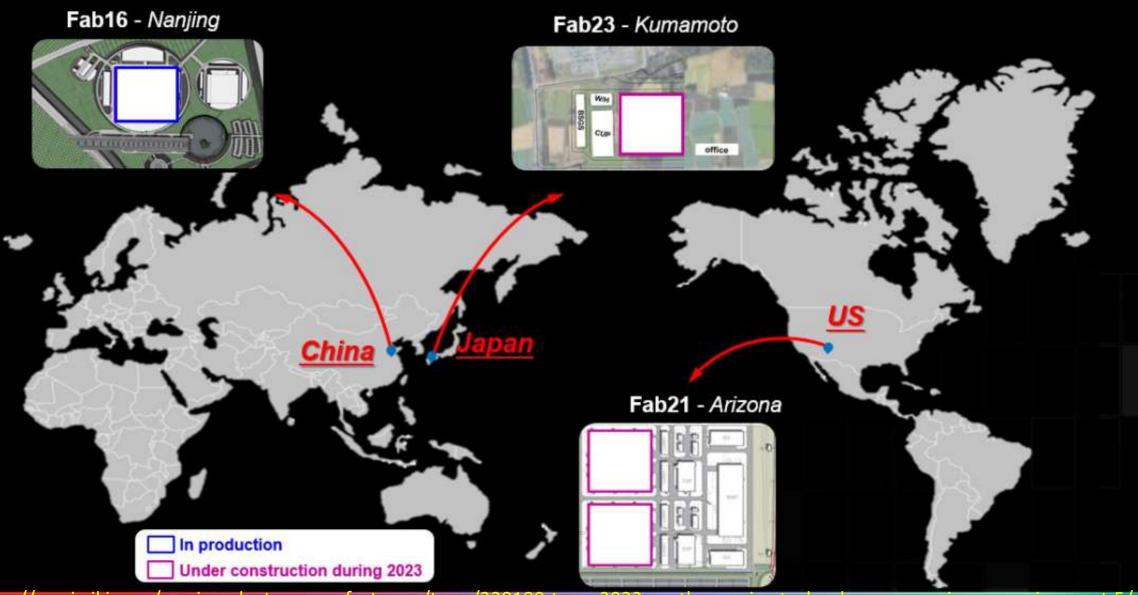

# **Expanding Global Footprint for 12" Fabs**

# Agenda

- Introduction

- Semiconductor R&D Trends

- Transistor Scaling

- Materials and Devices

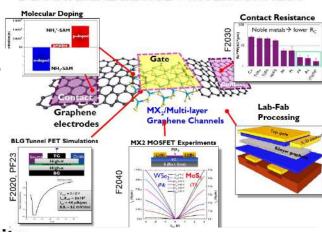

# **Energy-efficiency and Performance Innovation of Chips with 2-Dimensional Materials (EPIC 2-D Materials)**

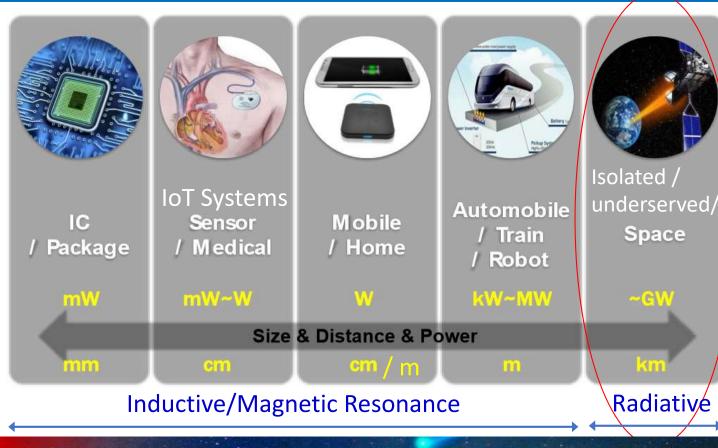

Energy-efficient MetaConductors for Convergence of Sustainable Electronics (E-MC2 of Sustainable Electronics): \$750k (Phase I Y1), \$5M (Target Y2-Y3)

#### **Revolutionizing the Semiconductor Industry**

Our **metaconductors** help the electronics industry achieve high performance computing with 200% power efficiency improvement.

#### **Wireless Power Transfer**

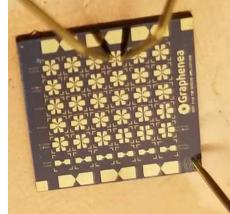

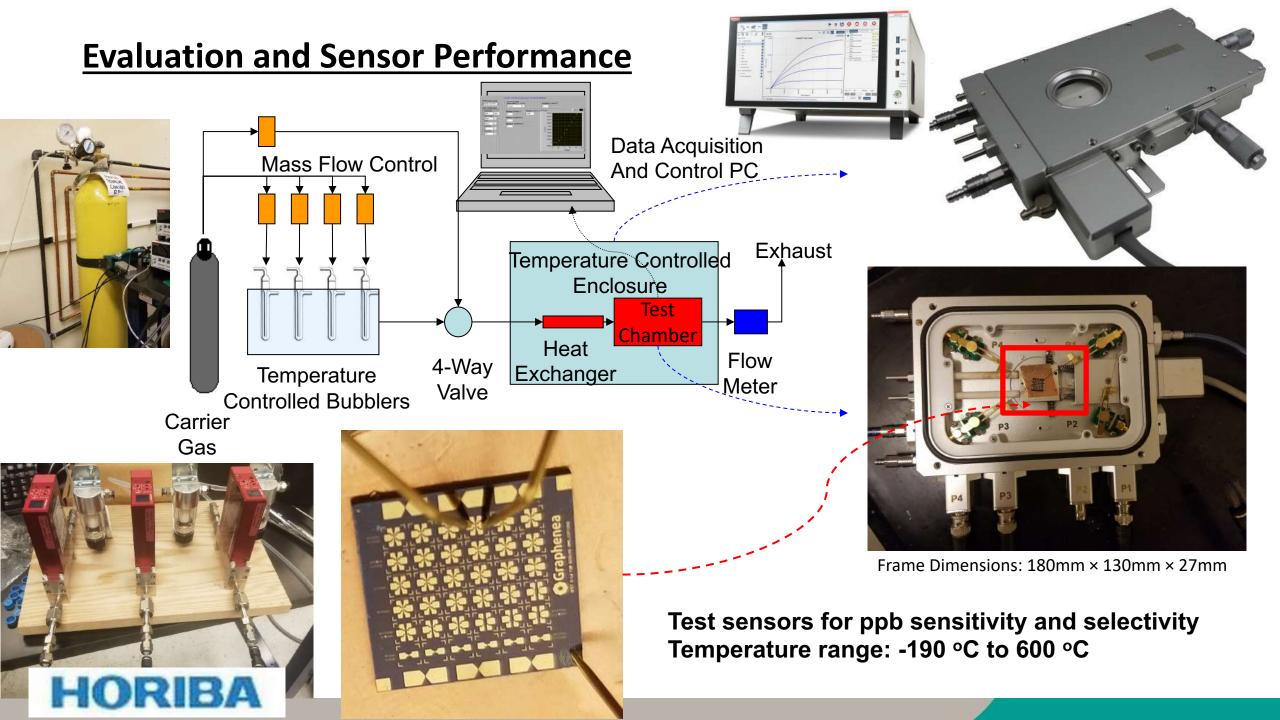

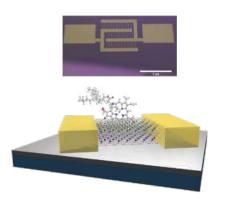

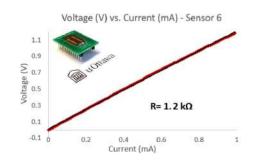

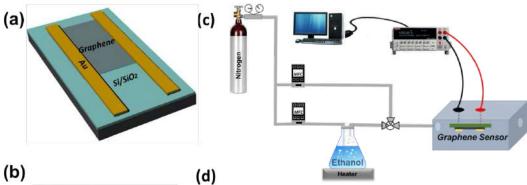

# Sensitive detection and identification of airborne chemicals and biological agents

2D materials FET response in different environments

• Light matter interaction for selectivity

• Device miniaturization, connectivity, packaging etc.

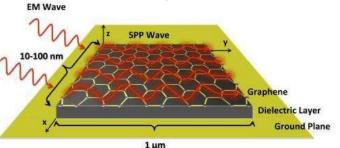

#### **Graphene Roadmap**

**High-Performance** Computing

2-D MATERIAL DEVICE + INTERCONNECT

**Smart Sensors**

Processing Challenges

0.1

Low-cost RF Circuits Mid-performance (GHz)

= 16 GHz

Supercapacitors

Stainless steel plate

Stainless steel plate Current Collector

**Optoelectronics Devices**

Flexible antennas in consumer

Transparent electrodes

⁴10 Gbit/s

Fraquency (GHz)

· 'Graphene' was first isolated in the lab by Professor Andre Geim with former student Konstantin Novoselov at the University of Manchester, England in 2004

(Both were later Knighted, twice)

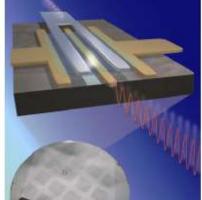

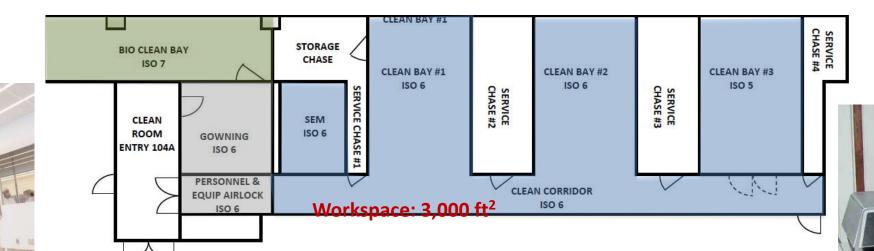

#### **Davidson Foundation Cleanroom**

Mask aligner

Image Source: University of Nevada, Reno

# Thank you for your support